Companies Pushing Open Source RISC-V Silicon Out to the EdgeCompanies Pushing Open Source RISC-V Silicon Out to the Edge

It emerged as a force in the silicon market last year, and its been gaining momentum ever since.

May 28, 2019

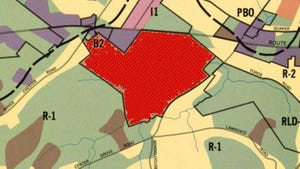

In 2018, the open source instruction set architecture RISC-V emerged as a force to reckon with in the hard-to-crack silicon market. The ball got started early last year, when SiFive, a Silicon Valley startup built around the open silicon design, quickly sold out on a limited run of a single-board computer for RISC-V developers, HiFive Unleased, that it offered on a crowdfunding site for the premium price of $999 apiece, resulting in gross sales of $143,700.

That was followed by an announcement a month later that the hard-drive maker Western Digital, had signed a multi-year license for SiFive's Freedom Platform and become an investor in the company.

Western Digital is "shifting their entire product line, which is currently shipping about a billion cores a year," SiFive's CEO, Naveed Sherwani, told Data Center Knowledge at the time. "They expect that to become, in a few years, two billion cores a year. They have made a public commitment that in a couple of years Western Digital is going to shift its entire product line onto RISC-V."

The reduced instruction set architecture (pronounced "risk-five") is becoming increasingly attractive to hardware manufacturers, especially those building embedded IoT or edge devices. Like Arm processors, the architecture only requires a small amount of power when compared to x86 devices from Intel or AMD, with some benchmarks indicating it's even more energy efficient than Arm, which has become the gold standard for battery-operated devices.

The major advantage of the ISA (Instruction Set Architecture) over Arm, however, is that RISC-V is open source. OEMs can use the specification to design and manufacture chips paying little to no royalties, which is a large part of the price of bringing an Arm chip to market. Some users also find further advantage in RISC-V's "permissive" BSD licensing, which means customized RISC-V chips can be made proprietary for IP protection, if desired.

It's also an all-new design, the result of what started as a 2010 summer project at UC Berkeley, and so avoids some of the problems that are baked into older processor designs. The project looks like it's here to stay, as its garnered support and uptake from major industry players, including Google, Samsung, IBM, Nvidia, and Qualcomm, among others.

Growing the RISC-V Ecosystem

So far this year, the pace of news coming from the RISC-V community has accelerated, starting with a January announcement from the RISC-V Foundation, the non-profit organization created to standardize and promote the architecture, that Martin Fink, Western Digital's CTO, had been appointed to fill a newly created CEO role until a permanent replacement could be found.

"Things keep growing faster than we ever predicted," said SiFive co-founder and chief architect Krste Asanovic, speaking in his role as the RISC-V Foundation board chair. He was the lead developer of the original UC Berkeley team behind RISC-V.

"We see that there's massive opportunity all around the world to do things, and we felt we needed bold leadership from somebody who can come in and grow the foundation," he added. "Before outstripping the current capacity of the foundation, we need to add more people to help drive growth. There's a lot of interest worldwide, a lot of excitement. We want to try and harness that in the best way possible."

On March 12 it was announced that Calista Redmond, VP of IBM's Z ecosystem for mainframes, was getting the job. She came to the table as a 12-year veteran at Big Blue, and also as a former board member of the Linux Foundation's Open Mainframe Project.

Her connection to the Linux Foundation seems to have come with an immediate benefit for RISC-V developers. On the day before her appointment to the CEO role at the RISC-V Foundation was announced, the software-focused Linux Foundation said it was making a move into the hardware realm with the creation of the CHIPS Alliance, a project tasked with hosting implementation efforts around the RISC-V architecture, with an initial membership roll that included SiFive, Esperanto Technologies, Western Digital, and Google.

For its part, Google contributed to the alliance the Universal Verification Methodology environment (for verifying architectural and micro-architectural designs) it had been developing. The company has since doubled down on it's RISC-V investment, with an announcement this month that it was taking a seat on the board of lowRISC, another RISC-V non-profit with a mandate to "to develop and maintain open source silicon designs and tools." Google had already been involved with lowRISC, in a collaboration that included ETH Zürich (also known as the Swiss Federal Institute of Technology in Zurich), to develop and release the "Ibex" RISC-V core.

Other core releases have been in the news this year. Most notably, Western Digital's open source release in January of the 32-bit SweRV Core EH1 developed for use in its upcoming products. According to Western Digital, the core is designed for embedded devices running data-intensive applications, such as storage controllers, industrial IoT devices, real-time analytics in surveillance systems, and the like. Typical for RISC-V, the processor sips power and clocks in at up to 1.8Ghz while running on a 28nm CMOS battery.

In addition, Western Digital open sourced its SweRV ISS instruction set simulator software to ensure RISC-V cores are executing instructions properly.

Bringing RISC-V to Market

While companies such as Western Digital and Google have the expertise and funds to design and manufacture RISC-V chips to suit their needs, that model isn't what's driving the market. Many of the companies deploying RISC-V chips are smaller organizations, some of them startups, seeking to escape the expenses associated with licensing and manufacturing silicon from Arm, or attempting to shoehorn in off-the-rack chips from Arm suppliers. For the most part, they have little to no experience in chip design or navigating the labryinth of turning designs into silicon.

That's where companies such as Cortus and SiFive, both founding members of the RISC-V foundation, come into play. They offer design templates that can be modified to meet specific needs, along with the expertise necessary to turn designs into functioning products.

In March, France-based Cortus announced general availability of a family of six RISC-V processors that its customers can use to design into application-specific integrated circuits.

"I am delighted to see so many products using the RISC-V ISA," Michael Chapman, Cortus's president and CEO, said in a statement at the time. "Our customers are embracing this architecture of the future. RISC-V is becoming a real industry standard."

San Francisco-based SiFive, founded by three of the original developers of the ISA at UC Berkeley, was the first company to produce a chip implementing the RISC-V ISA. It continues to lead the way and has been working to shorten the time-to-market for those using its services. In April it announced something of a breakthrough, when human-interface designer Synaptics was able to design a chip based on SiFive's E2 Series Core IP in only two months.

"SiFive's Core Designer allowed our design team to get direct, hands-on access much earlier in the process and enabled us to rapidly optimize our configuration," Prashant Shamarao, Synaptics' VP of product development, said in a statement.

Around the same time, SiFive launched its S2 Core IP Series, a 64-bit addition to its 2 Series Core IP, targeted primarily at embedded devices at the edge. The company is billing the silicon as "the world’s smallest commercial 64-bit embedded core" and says the chips are half the size of a similarly configured S5 core.

"The ever-growing number of connected devices with artificial intelligence, machine learning, IoT, and real-time workloads have generated a massive demand for greatly enhanced embedded intelligence in compute at the edge," the company said in a statement. "Legacy architectures have long ignored the need for small, efficient, 64-bit, real-time embedded processors."

RISC-V's success with the open source approach is also being noted by others in the silicon business. Wave Computing, which licenses the MIPS RISC architecture that was popular in the '80s and '90s but has been eclipsed by Arm, announced it would seek to breathe new life into its aging design by making it open source. In March, the company announced that release 6, MIPS's latest version, was available under an open source license covering both 32-bit and 64-bit implementations.

About the Author

You May Also Like